仿真的概念

完成了设计输入以及成功综合、布局布线之后,只能说明设计符合一定的语法规范。但是是否满足要求的功能,是不能保证的,还需要通过仿真流程对设计进行验证。仿真的目的就是在软件环境下,验证电路的行为和设想的行为是否一致。

仿真分为功能仿真和时序仿真。

- (1)功能仿真(行为仿真,前仿真)

功能仿真是在设计输入之后,还没有综合、布局布线之前的仿真,又称为行为仿真和前仿真。此阶段不考虑电路的逻辑门和寄存器之间的信号传播延时,仅考虑理想状态下,电路行为是否与设想的一致。如果设计功能都不能满足,其他环节都无从谈起。

使用modelsim进行功能仿真需要的文件:

- 功能模块.v

- 测试激励.vt // test bench

- (2)时序仿真(后仿真)

但是,仅仅功能仿真是无意义的,还需要时序仿真,亦称为后仿真,是指在综合、布局布线之后,考虑到电路已经映射到特定的工艺环境之后和器件延时的情况下对布局布线的网表文件经进行的仿真。其中器件延时信息是通过反标时序延时信息来实现的。如果在时序分析中发现时序不满足需要,而更改代码,则功能仿真必须更新进行。

使用modelsim进行功能仿真需要的文件:

- 功能模块.v

- 测试激励.vt // test bench

- 标准延时文件.sdo //声明电路和门延时标准

- 功能模块.vo //映射到布局布线之后的电路

- 自定义的延时文件.sdf //这个是可选的,自行编写器件延时标准进行仿真, 即是上文提到的反标时序延时信息。

对于目前主流的altera FPGA器件而言,时序仿真已经被静态时序分析取代。 只需要进行功能仿真,确保电路行为与预想的一致, 实际电路的走线延时/亚稳定状态的问题交给STA(static timing analysis)来处理,通过timing report来分析和改善,不需要再人为的观看仿真的波形,排查时序问题。

modelsim的使用

在此仅说明modelsim软件的使用方式,至于test bench激励文件的编写不做介绍。

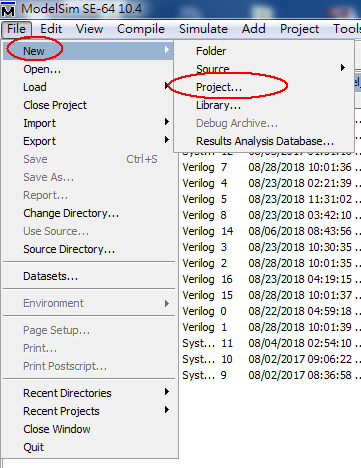

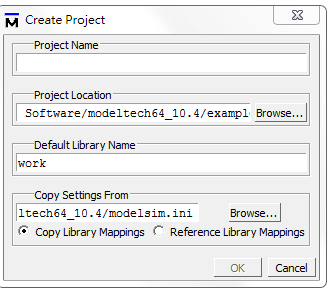

- 首先创建一个 modelsim的project。 File –> new –> project

- 请注意modelsim的这个project和quartus的project毫无关系,可以按自己的喜好命名、设置存放位置。

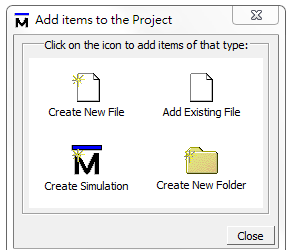

- 添加要进行仿真的模块文件,包括.v和.vt

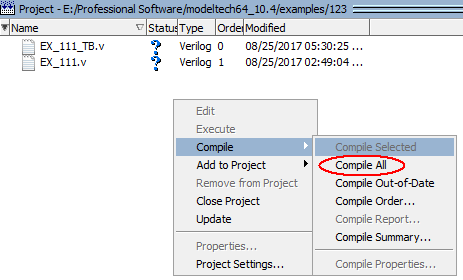

- 右键,编译文件。

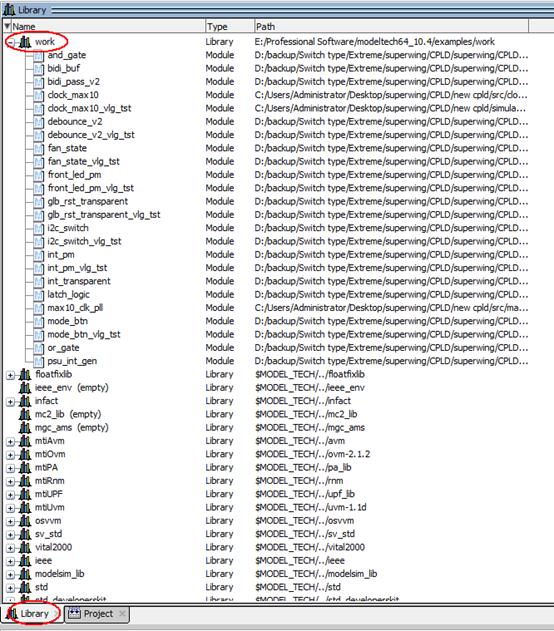

- 通过之后会在library的工作区中看到你添加进来的文件中包含的模块

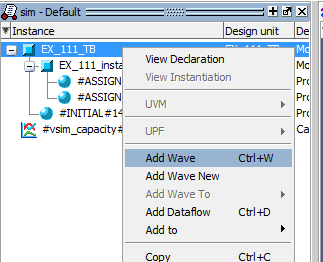

- 选择对应的测试模块,右键 simulate without optimization

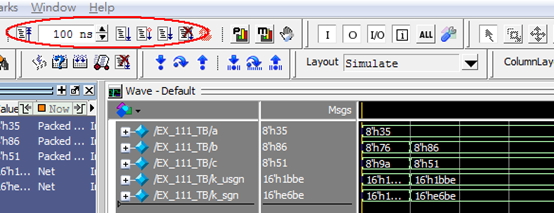

- 在新出现的sim目录中,右键add wave,将对应信号放到waveform视图中。

- 根据自己的需要,开始run并观察波形